LAPORAN AKHIR MODUL 2 PERCOBAAN 1

Laporan Akhir Percobaan 1

2. Alat dan bahan[Kembali]

- Proteus Versi 8.13

- J-K flip flop

Kelebihan J-K Flip-flop adalah tidak adanya kondisi terlarang atau yang berarti diberi berapapun inputan asalkan terdapat clock maka akan terjadi perubahan pada keluaran atau outputnya.

3. D flip flop

D Flip-flop merupakan salah satu jenis flip-flop yang dibangun dengan menggunakan flip-flop R-S. Perbedaan dengan R-S flip-flop terletak pada inputan R, dan D Flip-flop inputan R terlebih dahulu diberi gerbang NOT.

3. Rangkaian Simulasi[Kembali]

4. Prinsip Kerja[Kembali]

Prinsip kerja dari rangkaian tersebut yaitu :

Pertama ,Input D flip-flop adalah nilai yang akan disimpan ketika sinyal clock (CLK) diterapkan.

Dalam gambar, terlihat ada input "0" dan "1" di sebelah kiri yang mungkin digunakan sebagai input data ke D flip-flop melalui saklar yang bisa mengatur input menjadi "0" atau "1". Ketika sinyal clock diberikan (transisi naik dari 0 ke 1), D flip-flop akan menyimpan nilai yang ada pada input D.

Kedua , JK flip-flop memiliki dua input, J dan K, dan dalam kasus ini, input J adalah "1" dan K adalah "0", yang mungkin dikontrol melalui saklar juga. J-K flip-flop berbeda dari D flip-flop karena outputnya dipengaruhi oleh kombinasi input J dan K:

Jika J = 1 dan K = 0, output akan menjadi 1 (set).

Jika J = 0 dan K = 1, output akan menjadi 0 (reset).

Jika J = 1 dan K = 1, output akan toggle (berubah dari 0 ke 1 atau sebaliknya).

Sama seperti D flip-flop, output akan diperbarui ketika sinyal clock diberikan.

Lalu , Saklar yang ditampilkan digunakan untuk mengontrol input ke flip-flop dan menampilkan outputnya. Lampu-lampu di sekitar saklar mungkin digunakan sebagai indikator status logika (0 atau 1) yang menunjukkan apakah input atau output dalam keadaan tinggi (1) atau rendah (0).

5. Video Praktikum[Kembali]

Percobaan 1:

Analisa Input dan Output pada masing masing kondisi , buatkan prosesnya menggunakan rangkaina dalam masing masing flip flop .

jawab :

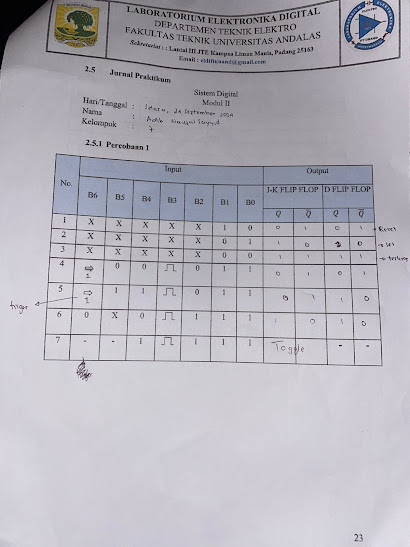

- Pada kondisi 1 yang dimana input dari B6, B5, B4, B3, B2, yaitu x yang artinya bebas, B1 = 1, B0 = 0, maka output pada J-K Flip-Flop yaitu Q = 0, Q = 1, dan output dari D Flip-Flop yaitu Q = 0 dan Q = 1, maka terjadilah kondisi reset.

- Pada kondisi 2 yang dimana input dari B6, B5, B4, B3, B2, yaitu x (bebas inputannya), B1 = 0, B0 = 1, maka output pada J-K Flip-Flop yaitu Q = 1 dan Q = 0, dan output dari D Flip-Flop yaitu Q = 1 dan Q = 0, maka terjadilah kondisi set.

- Pada kondisi 3 yang dimana input dari B6, B5, B4, B3, B2, yaitu x (bebas inputannya), B1 = 0, B0 = 0, maka output pada J-K Flip-Flop yaitu Q = 1 dan Q = 1, dan pada rangkaian D Flip-Flop yaitu Q = 1 dan Q = 1, maka kondisi tersebut keadaan terlarang.

- Pada kondisi 4 yang dimana diberikan inputan B6 = 1 sebagai trigger, B5 = 0, B4 = D, B3 = clock, B2 = 0, B1 = 1, B0 = 1, maka output pada rangkaian J-K Flip-Flop yaitu Q = 0 dan Q = 1, dan output pada rangkaian D Flip-Flop yaitu Q = 0 dan Q = 1.

- Pada kondisi 5 yang dimana diberikan inputan B6 = 1 sebagai trigger, B5 = 1, B4 = 1, B3 = clock sebagai pemicu, B2 = 0, B1 = 1, B0 = 0, maka output yang dihasilkan dari input tersebut terhadap rangkaian J-K Flip-Flop yaitu Q = 0, Q = 1, dan pada rangkaian D Flip-Flop yaitu Q = 1 dan Q = 0.

- Pada kondisi 6 yang dimana diberikan inputan B6 = 0 dan B5 = x (bebas inputannya), B4 = 0, B3 = clock yang dijadikan sebagai pemicu, B2 = 1, B1 = 1, B0 = 1, maka output yang didapatkan pada rangkaian J-K Flip-Flop yaitu Q = 1 dan Q = 0, dan pada rangkaian D Flip-Flop Q = 1 dan Q = 0.

- Pada kondisi 7 yang mana inputan B6 dan B5 tidak terhubung pada rangkaian D-Flip-Flop, lalu B4 = 1, B3 = clock sebagai pemicu, B2 = 1, B1 = 1, B0 = 1, maka output pada rangkaian J-K yang selalu berubah-ubah outputnya dikarenakan clock. Jadi kondisi tersebut dinamakan Toggle, dan output pada rangkaian D-Flip-Flop tidak ada karena tidak ada inputan yang terhubung.

7. Download[Kembali]

Komentar

Posting Komentar